# Making Consistent Contacts to Graphene: Effect of Architecture and Growth Induced Defects

Krishna Bharadwaj B, Rudra Pratap, and Srinivasan Raghavan\*

Center For Nanoscience and Engineering, Indian Insitute of Science, India

E-mail: sxraghavan@gmail.com

#### **Abstract**

The effect of contact architecture, graphene defect density and metal-semiconductor work function difference on resistivity of metal-graphene contacts have been investigated. An architecture with metal on the bottom of graphene is found to yield resistivities that are lower, by a factor of 4, and most consistent as compared to metal on top of graphene. Growth defects in graphene film were found to further reduce resistivity by a factor of 2. Using a combination of method and metal used, the contact resistivity of graphene has been decreased by a factor of  $10 \text{ to } 1200 \pm 250 \,\Omega\mu\text{m}$  using Palladium as the contact metal. While the improved consistency is due to the metal being able to contact uncontaminanted graphene in the metal on the bottom architecture, lower contact resistivities observed on defective graphene with the same metal is attributed to the increased number of modes of quantum transport in the channel.

#### Introduction

In graphene devices, the metal-graphene contact resistivity is a limiting factor in various applications.  $^{1,2}$  Particularly in the case of radio frequency devices and ultra low power sensor applications, ohmic contacts with resistivity in the range of 0.2-1 k $\Omega\mu$ m are desirable.  $^3$  Contact resistivity

<sup>\*</sup>To whom correspondence should be addressed

values as low as 200-500  $\Omega\mu$ m have been reported on exfoliated graphene and devices of small dimensions ~100 nm). However, on the technologically relevant Chemical Vapor Deposition (CVD) grown graphene, the reported values are comparatively higher (0.5-10<sup>4</sup>  $\Omega\mu$ m<sup>2,4-9</sup>). Several methods have been employed to reduce the contact resistivity in CVD graphene devices. These include the uses of a sacrificial Al layer, <sup>10</sup> double contacted geometry, <sup>11</sup> UV-Ozone treatment, <sup>2</sup> Ni catalyzed etching <sup>12</sup> and localized plasma treatment/argon bombardment. <sup>13</sup> Absolute values as low as ~500  $\Omega\mu$ m have been reported. However, from a device engineering perspective it is not only the absolute value of contact resistivity that is important but also the consistency in resistivity values achieved by a given method of contact formation. To illustrate the current state, a summary of the literature on the contact resistivity of Au-contacted graphene (Au is the most commonly used contact) on Si/SiO2 and the scatter in the reported values are shown in the Fig. S1 of supplementary material. Large scatter in the measured values of contact resistivity, as seen from the plot, is a common feature of measurements on graphene devices. For instance, a scatter of up 10<sup>4</sup>(!) between reports using the same metal-graphene combination <sup>2,4-9</sup> as well as between devices in the same report have been observed.

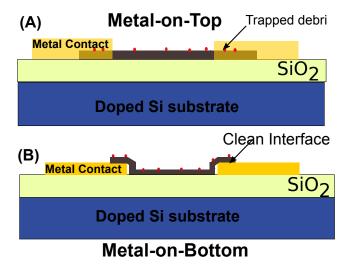

The contact resistivities reported in the literature are typically measured by using what we refer to in this letter as metal-on-top architecture (MOTA). Fig. 1.(A) shows MOTA device schematics. This architecture has its origins in the fact that graphene research started with micron sized exfoliated monolayer flakes on a SiO<sub>2</sub>/Si substrate whose physical location had to be optically identified prior to further lithographic processing. <sup>14</sup> The contacts are then made on top of these flakes using electron beam assisted lithographic processes. This fabrication flow is susceptible to there being trapped photo-resist debris between the graphene and the metal leading to spurious contacts <sup>12,15</sup> thereby leading to large variations ( $10^3 \ \Omega \mu m^4$ ) in the observed contact resistivity. With the advent of large area monolayer graphene grown by CVD, <sup>16</sup> the constraint of having to first identify location is removed, allowing one to explore newer architectures such as the metal-on-bottom contact architecture (MOBA) contact topology used in the current study (Fig. 1.(B)). We show that by using MOBA, consistent contacts can be obtained with resistivities that are lower, than those

obtained on MOTA, by a factor of 4.

This effort at obtaining consistent contacts was initiated to ensure that a study on the effect of growth defects on the contact resistivity of CVD graphene is statistically relevant. Their effect on contact resistivity has been largely ignored. Though recent reports on artificially created defects using ion bombardment methods and nano-particle based etching processes are available,  $^{12}$  they either require complicated processing steps or lack precise control on creating defects. We show that in addition to reducing the metal-semiconductor barrier height, the growth induced defect density of the graphene film also helps to reduce contact resistivity. A reduction in contact resistivity by a factor of 2 is observed in this study for three of the most commonly used metals Au, Pt and Pd. Thus, by using a combination of metal and method, a reduction in resistivity by a factor of 10 to values as low as  $1200 \pm 250 \ \Omega \mu m$  is demonstrated within a controlled set of experiments. As shown in the supplementary material, this is one of the best combinations yet reported.

Figure 1: (A) MOTA or Metal-on-top architecture. (B) Metal-on-bottom architecture. The detailed process flow and figures are included in the supplementary material. The MOBA process flow precludes the possibility of there being process debri between the metal and graphene.

## **Experimental methods**

Graphene was grown on Cu foil using CVD in two different conditions as described in the supplementary material. During graphene growth, two different defect densities were obtained by controlling the source flow conditions as described by ?. Post CVD, PMMA (950 A4) was spin coated on the graphene covered Cu substrate and underlying Cu was etched using ammonium per sulphate solution. Following Cu etch, the PMMA-graphene composite was further processed by two different methods to yield the MOBA and MOTA architectures as described below.

For device fabrication a heavily p-doped Si wafer with 300 nm SiO<sub>2</sub> capping was used as the initial substrate. For the MOBA, metal electrodes were first patterned on the substrate using standard optical lithographic lift-off processes as shown in supplementary material Fig. S3. A mild oxygen plasma treatment was performed to remove photo resist residues and provide a clean surface to contact graphene. The graphene polymer composite was transferred on top of these patterned metal pads to yield bottom contacted graphene. Since, the metal surface on which graphene is transferred has never been covered by polymer at any stage in processing, this contact architecture provides cleaner metal-graphene interface. After drying at room temperature for 8 hrs, a soft bake on a hot plate at 180°C in air was done to remove trapped water and improve adhesion. The PMMA support layer was finally removed with an overnight acetone etch thereby yielding MOBA contacts. In the MOTA process, graphene was first directly transferred on top of a clean SiO<sub>2</sub> surface using the PMMA support layer as described previously. Following PMMA removal using acetone, metal pads and graphene channel were patterned using standard lithographic procedures as described in the supplementary material.

#### **Results and Discussion**

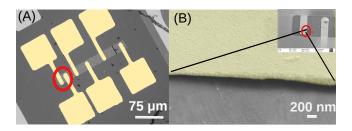

Transfer length measurement structures are typically used to measure the contact resistivity of metal semiconductor junctions. <sup>18</sup> Graphene channels of varying lengths were fabricated as shown in Fig. 2.(A). The channels were made 25  $\mu$ m wide to average the statistical variations in the number of grains (usual grain sizes were 2-5  $\mu$ m as shown in the supplementary material) and the device lengths were varied from 10  $\mu$ m to 50  $\mu$ m in 5 steps. Since, in MOBA, the graphene is transferred onto the metal contact pads, which are usually 100 nm thick, it is important to examine

the region, (see encircled in red (online only) in Fig. 2 in which graphene monolayer comes off the metal surface contacts onto the wafer to ensure that there are not tears there. SEM image of this region is shown in Fig. 2.(B). In the inset, graphene is seen in dark contrast with the bright metal layer at the bottom. Due to the thick support layer of PMMA used during transfer, graphene remains intact and is defect free in this region. Also, it is important to note that graphene contacts the SiO<sub>2</sub> layer within 200 nm from the metal side wall making the suspended graphene region negligible, in comparison with the large channel lengths considered.

Figure 2: Device Representation:(A) Typical TLM structure fabricated using the MOBA. 25  $\mu$ m wide channels are fabricated with lengths varying from 10  $\mu$ m to 50  $\mu$ m. (B) A magnified image of the metal-SiO<sub>2</sub> interface (see text for discussions). No tears are visible.

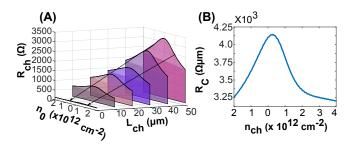

With the heavily doped Si as the bottom gate, each pair of electrodes in the TLM structure serves as a source-drain contact to the graphene field effect transistors (gFET) giving rise to a gated TLM structure. Due to the nonexistent band gap and a continuously gate tunable channel carrier concentration (and hence the Fermi energy,  $E_f$ ), a gate voltage dependent contact resistivity is expected, <sup>19</sup> though instances of gate-independent contact resistivities have also been reported. <sup>20</sup> Two terminal channel resistivity vs. gate voltage ( $V_G$ ) characteristics of the individual gFETs with varying lengths that constitute the TLM structure are plotted in Fig. 3.(A), with the longest one having the highest resistance. All the devices showed clear p-type behavior (indicated by the positive charge neutrality point (CNP) and the corresponding gate voltage  $V_{CNP}$ ) as is usually the case in CVD grown graphene due to unintentional doping. <sup>21</sup> The CNP and corresponding gate voltage  $V_{CNP}$  of all the devices were close but not coincident and were in the range of 15-20 V (on a 300 nm oxide, 15 V translates to 0.5 MV/cm). The uniform and monotonic shift in CNP at different channel lengths (shown in the Fig S3 of supplementary material) clearly indicates a

uniform doping density in graphene, a hallmark of CVD grown films. To account for the non-coinciding  $V_{CNP}$  in the different devices, the contact resistivity of the entire TLM structure was extracted as a function of the carrier concentration  $(n_{ch})$  derived using Eq. (1), where  $C_{ox}$  is the gate oxide capacitance,  $n_0$  is the intrinsic carrier concentration and  $n_G$  is the gate dependent carrier concentration, as opposed to the normally used gate voltage. Fig. 3.(A) stacks the R- $n_{ch}$  plots of all the devices in the TLM structure. The black lines connect the resistivity values obtained at the same  $n_{ch}$  on various devices and are extrapolated to obtain the contact resistivity. The extracted contact resistivity in  $\Omega\mu$ m is shown in the Fig. 3.(B).

$$n_{\rm ch} = n_0 + n_G \tag{1a}$$

$$n_G = (V_G - V_{CNP}) * C_{ox}/q \tag{1b}$$

$$\rho_{ch} = \frac{1}{\sqrt{n_0^2 + n_G^2} * \mu} \tag{1c}$$

Figure 3: Carrier density adjusted TLM: (A) Channel resistance  $R_{ch}$  of gFETs (made using Au contact pads) having different channel lengths  $L_{ch}$  are plotted against gate dependent carrier concentration  $n_0$ . Straight line fits made to resistances at the same carrier concentration are used to extract the contact resistance  $R_C$  (in  $\Omega$ , which is later multiplied by width to obtain resistivity) by using the Y-intercept. (B) The contact resistivity so extracted.

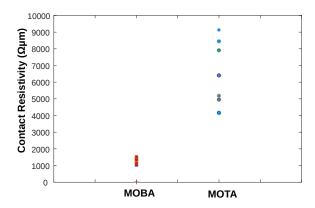

Figure 4 compares the contact resistivity, when Au is used as the contact metal, extracted at zero gate voltage from the TLM structures fabricated using MOTA and MOBA. The values obtained using similar graphene (from the same growth condition) on MOBA was not only four folds lower in the absolute magnitude, but also in the standard deviation. This indicates that, the

'graphene-last' fabrication process, used in MOBA, significantly reduces the contamination and lithographic residues at the metal-graphene interface, thereby enabling better consistency in the observed values.

Figure 4: Effect of MOBA vs. MOTA on contact resistivity measured using Au contact pads and at zero gate bias. MOBA not only has lower contact resistivity, but also better consistency in the observed values.

While the lowest reported contact resistivity in ex-foliated graphene is  $128~\Omega\mu\text{m}$ ,  $^{22}$  the typical reported values using CVD grown graphene with Au is  $790\pm300~\Omega\mu\text{m}$ , both using MOTA. The lowest absolute contact resistivity obtained in this work is  $1200\pm250~\Omega\mu\text{m}$  and it compares reasonably well with the usually reported values ((1000-10000)  $\Omega\mu\text{m}$ ) in the literature. However, a low overall contact resistivity was not the objective of this work. Rather it was the comparison between bottom and top contacts obtained on the same platform and the effect of graphene defects. Since, in the previous section, the bottom contacted devices showed better consistency in the observed values, MOBA architecture was used to observe the effect of defect density and metal work function difference on the contact resistivity as described below.

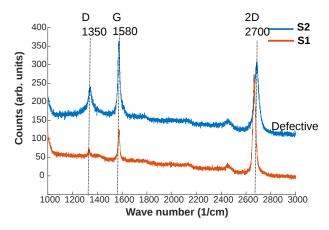

The effect of graphene growth defect density on the contact resistivity has been a hitherto unexplored area despite its obvious practical importance in devices. Graphene films having different defect densities were grown by controlling the source flow conditions as described in the supplementary material, and the Raman spectroscopic studies obtained on the defective sites on two different samples used ( $S_1$  and  $S_2$ ) are shown in Fig. 5. The 'D' peak at 1350 cm<sup>-1</sup> ('D' peak) qualitatively indicates the number of defects in the graphene sample.<sup>24</sup> A simple comparison of

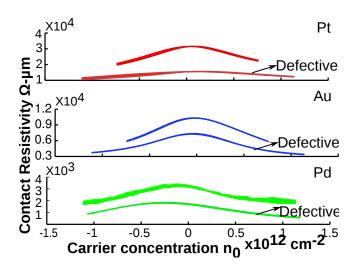

the peak intensities indicate that  $S_2$  has a higher defect density. From the expression developed by ?, it is seen that  $S_2$  has an order of magnitude higher defect density than  $S_1$ . The three most commonly used metals, namely Pt, Au, and Pd with work functions  $5.65 \, \text{eV}$ ,  $5.40 \, \text{eV}$ , and  $5.22 \, \text{eV}$  respectively were chosen to fabricate devices using the two kinds of graphene. Figures 6 shows the contact resistivity extracted from TLM measurements. It can be seen that irrespective of the metal used, contact resistivity is lower when the graphene film is defective by a factor of 2. In contrast, the sheet resistance increases with defect density, making the inverse dependence of contact resistivity on defect density, an intriguing observation. From the  $I_D$ - $V_G$  of the individual devices, the field effect mobility was extracted and the residual carrier concentration was calculated using equation Eq. (1) (details on the extaction and fit are presented in the supplementary material). Comparing the values obtained using the constant mobility fit, it was seen that the sample  $S_2$  with higher defects has a mobility of  $1200 \, \text{cm}^2/\text{V} \cdot \text{s}$  and a intrinsic carrier concentration of  $1E13 \, \text{cm}^{-2}$ , while sample  $S_1$  had a mobility of  $16310 \, \text{cm}^2/\text{V} \cdot \text{s}$  and a carrier concentration of  $2.5E12 \, \text{cm}^{-2}$ .

Figure 5: Raman spectrum obtained on samples  $S_1$  and  $S_2$ . The 'D' peak intensity, which can be used to quantitatively determine the defect density indicates an order of magnitude higher defect density in  $S_2$  than in  $S_1$ .

Figure 6: Effect of metal work function and graphene defect density on contact resistivity. The contact resistivity obtained at carrier concentration varying from  $-1.5 - 1.5 \times 10^{12} \, \mathrm{cm}^{-2}$  are plotted for three metals namely Pt, Au and Pd in decreasing order of their metal work functions. The values with the standard deviation are displayed as bands in each plot. For each metal, the contact resistivity of graphene with two different defect densities are plotted. From the figure it is clearly seen that under the same metal, the graphene with higher defect density has a lower resistivity. Moreover, under this architecture, the resistivity shows a linear relation with the metal work function.

The contact conductivity  $(G_c)$  of graphene has been modeled by Xia et al. <sup>19</sup> as follows,

$$G_c = (4e^2/h)TM_{total} (2a)$$

$$M = (\Delta E_f / \pi \hbar V_f) W \tag{2b}$$

$$M_{total} = M_{VG} + M_{CNP} (2c)$$

$$M_{CNP} = (E_{ex}/\pi\hbar V_f)W \tag{2d}$$

$$E_{ex} = \hbar v_f \sqrt{\pi n_0} \tag{2e}$$

where M is the quantum number of modes on graphene, T is the transmission probability from metal to graphene in the bulk, e is the electronic charge,  $E_F$  is the Fermi level at a given gate voltage and  $E_{ex}$  is the Fermi level of intrinsic graphene,  $V_f$  is the Fermi velocity,  $\hbar$  is the reduced planks constant, and W is the channel width. The quantum number of modes in graphene M is related to  $\Delta E_f$  as described in Eq. (??), where  $\Delta E_f$  is the energy difference between the actual

Fermi level in the system ( $E_F$ ) and charge nuetrality point energy ( $E_{CNP}$ ). In intrinsic graphene, the carrier concentration drops to zero at  $E_F = 0$  due to vanishing density of states, and the conductance drops to the minimum conductance level ( $\sigma = 2e^2/\hbar$ ). However, CVD grown graphene gets unintentionally doped and is usually defective leading to higher conductance at the CNP. This increased conductance at the CNP is due to additional number of conductance modes made available due to the defects in the sample. Hence the total number of modes in the graphene channel is  $M_{total} = M_{VG} + M_{CNP}$ , where  $M_{VG}$  is the number of modes at a particular  $E_F$ , obtained as described before and  $M_{CNP}$  is the number of modes in the channel due to the presence of defects. If the carrier concentration at CNP ( $n_0$ ) is known, the excess number of modes at CNP can be calculated as mentioned in equation set Eq. (2).

Using the residual carrier concentration extracted previously on both the samples and using the Eq. (2), the  $E_{ex}$  on the defective graphene was higher than the other by 0.3 meV, resulting in  $M_{CNP}(B) = 2 * M_{CNP}(A)$ . The contact resistivity ratio of the two samples with Pt at the CNP, as seen from the Fig. 6, was only slightly higher than 2 indicating that the change in number of modes(M) under the defective graphene could be the dominant reason for the reduction in the contact resistivity in defective graphene. However, it should be noted that introducing defects to reduce contact resistivity might adversely affect the device performance as the uniform distribution of defects in graphene has a degrading effect on the charge mobilities. 25 While such a method of reducing the contact resistivity would benefit sensing applications, whose sensitivity improves with defect density the film, high speed logic applications might be affected due to mobility degradation. Hence, it is important to choose the right defect density to be introduced in the material such that a right balance obtained between the channel resistance and the contact resistivity and thereby satisfying the application requirements. Since such an observation is not unique to graphene, but also many other 2D materials, these results hence offer an interesting route to further reduce contact resistivity to atomically-thin devices by selective defect engineering. Also, in the quest to find the most suitable material for graphene contacts, several metals have been previously explored in the literature. 7,10,26,27 There are considerable number of contradicting reports and there is no final

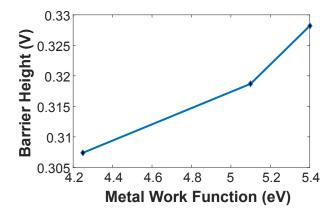

verdict on the best suited material for a given architecture. <sup>8,28</sup> As the effect of defects in graphene on the contact resistivity was largely ignored previously, it is possible that this might be the reason for the discrepancy. Figures 6 plots the contact resistivity vs. carrier concentration of graphene with various metals using MOBA. At the same carrier concentration, with the graphene being the same across different metals, Pd had the lowest contact resistivity among the three, followed by Au and Pt. Using a Schottky contact model between graphene and metal, the barrier height can be extracted as described by Schroder <sup>18</sup>. The linear relation between the barrier height (extracted from the Rc) and the metal work function shown in Fig. 7 indicates that thermionic emission is the dominating transport at the interface. <sup>29</sup>

Figure 7: Plot of barrier height vs. metal work function. Linear relation between the two indicates the thermionic emission being the prominent interface conductivity and thus, supporting the evidence that the contact resistivity is proportional to the work function difference

### **Summary**

In summary, we have extracted the contact resistivity of graphene using a minimal damage graphene-last fabrication process leading to a bottom contact architecture. This architecture results in very consistent contacts with low resistivities. The higher consistency allows a statistically relevant study of other effects such as defects on contact resistivity. It was seen that on all three commonly used materials namely Pt, Pd and Au, growth defects reduce contact resistivity by a factor of 2. Pt with the highest work function had the highest contact resistivity and Pd the lowest

#### References

- (1) Osman Balci and Coskun Kocabas. Rapid thermal annealing of graphene-metal contact. *Applied Physics Letters*, 101(24):243105, 2012.

- (2) Wei Li, Yiran Liang, Dangmin Yu, Lianmao Peng, Kurt P Pernstich, Tian Shen, AR Hight Walker, Guangjun Cheng, Christina A Hacker, Curt A Richter, et al. Ultraviolet/ozone treatment to reduce metal-graphene contact resistance. *Applied Physics Letters*, 102(18):183110, 2013.

- (3) Seul Ki Hong, Sang Chul Jeon, Wan Sik Hwang, and Byung Jin Cho. Resistance analysis and device design guideline for graphene rf transistors. *2D Materials*, 2(3):034011, 2015.

- (4) A Venugopal, L Colombo, and EM Vogel. Contact resistance in few and multilayer graphene devices. *Applied Physics Letters*, 96(1):013512, 2010.

- (5) Seung Min Song, Taek Yong Kim, One Jae Sul, Woo Cheol Shin, and Byung Jin Cho. Improvement of graphene metal contact resistance by introducing edge contacts at graphene under metal. *Applied Physics Letters*, 104(18):183506, 2014. doi: http://dx.doi.org/10.1063/1.4875709. URL http://scitation.aip.org/content/aip/journal/apl/104/18/10.1063/1.4875709.

- (6) K Nagashio, T Nishimura, K Kita, and A Toriumi. Metal/graphene contact as a performance killer of ultra-high mobility graphene analysis of intrinsic mobility and contact resistance. In *Electron Devices Meeting (IEDM)*, 2009 IEEE International, pages 1–4. IEEE, 2009.

- (7) Teng Ma, Wencai Ren, Zhibo Liu, Le Huang, Lai-Peng Ma, Xiuliang Ma, Zhiyong Zhang, Lan-Mao Peng, and Hui-Ming Cheng. Repeated Growth-Etching-Regrowth for Large-Area Defect-Free Single-Crystal Graphene by Chemical Vapor Deposition. ACS NANO, 8(12): 12806–12813, DEC 2014. ISSN 1936-0851. doi: {10.1021/nn506041t}.

- (8) Eiichiro Watanabe, Arolyn Conwill, Daiju Tsuya, and Yasuo Koide. Low contact resistance

- metals for graphene based devices. *Diamond and Related Materials*, 24(0):171 174, 2012. ISSN 0925-9635. doi: http://dx.doi.org/10.1016/j.diamond.2012.01.019. URL http://www.sciencedirect.com/science/article/pii/S0925963512000295.

- (9) Hua Zhong, Zhiyong Zhang, Bingyan Chen, Haitao Xu, Dangming Yu, Le Huang, and Lian-Mao Peng. Realization of low contact resistance close to theoretical limit in graphene transistors. 2014.

- (10) Allen Hsu, Han Wang, Ki Kang Kim, Jing Kong, and Tomas Palacios. Impact of graphene interface quality on contact resistance and rf device performance. *Electron Device Letters, IEEE*, 32(8):1008–1010, 2011. URL http://ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=5873116.

- (11) A.D. Franklin, Shu-Jen Han, A.A. Bol, and V. Perebeinos. Double contacts for improved performance of graphene transistors. *Electron Device Letters*, *IEEE*, 33(1):17–19, Jan 2012. ISSN 0741-3106. doi: 10.1109/LED.2011.2173154.

- (12) Wei Sun Leong, Hao Gong, and John T. L. Thong. Low-contact-resistance graphene devices with nickel-etched-graphene contacts. ACS Nano, 8(1):994–1001, 2014. doi: 10.1021/nn405834b. URL http://dx.doi.org/10.1021/nn405834b. PMID: 24328346.

- (13) Min Sup Choi, Seung Hwan Lee, and Won Jong Yoo. Plasma treatments to improve metal contacts in graphene field effect transistor. *Journal of Applied Physics*, 110(7):073305, 2011. doi: http://dx.doi.org/10.1063/1.3646506. URL http://scitation.aip.org/content/aip/journal/jap/110/7/10.1063/1.3646506.

- (14) A. K. Geim. Graphene: Status and prospects. *Science*, 324(5934):1530–1534, 2009. doi: 10.1126/science.1158877.

- (15) LeeEduardo J. H., Kannan Balasubramanian, Ralf Thomas Weitz, Marko Burghard, and

- Klaus Kern. Contact and edge effects in graphene devices. *Nat Nano*, 3(8):486–490, August 2008. ISSN 1748-3387. URL http://dx.doi.org/10.1038/nnano.2008.172.

- (16) Xuesong Li, Weiwei Cai, Jinho An, Seyoung Kim, Junghyo Nah, Dongxing Yang, Richard Piner, Aruna Velamakanni, Inhwa Jung, Emanuel Tutuc, Sanjay K. Banerjee, Luigi Colombo, and Rodney S. Ruoff. Large-area synthesis of high-quality and uniform graphene films on copper foils. *Science*, 324(5932):1312–1314, 2009. doi: 10.1126/science.1171245.

- (17) Paulo T Araujo, Mauricio Terrones, and Mildred S Dresselhaus. Defects and impurities in graphene-like materials. *Materials Today*, 15(3):98–109, 2012.

- (18) Dieter K. Schroder. *Semiconductor Material and Device Characterization*. Wiley-IEEE, 2006.

- (19) Fengnian Xia, Vasili Perebeinos, Yu-ming Lin, Yanqing Wu, and Phaedon Avouris. The origins and limits of metal-graphene junction resistance. *Nature nanotechnology*, 6(3):179–184, 2011.

- (20) S Russo, MF Craciun, M Yamamoto, AF Morpurgo, and S Tarucha. Contact resistance in graphene-based devices. *Physica E: Low-dimensional Systems and Nanostructures*, 42(4): 677–679, 2010. URL http://www.sciencedirect.com/science/article/pii/S1386947709005165.

- (21) Archana Venugopal, Jack Chan, Xuesong Li, Carl W Magnuson, Wiley P Kirk, Luigi Colombo, Rodney S Ruoff, and Eric M Vogel. Effective mobility of single-layer graphene transistors as a function of channel dimensions. *Journal of Applied Physics*, 109(10):104511, 2011. URL http://scitation.aip.org/content/aip/journal/jap/109/10/10.1063/1.3592338.

- (22) C. Malec and D. Davidović. Electronic properties of au-graphene contacts. *Phys. Rev. B*, 84: 033407, Jul 2011. doi: 10.1103/PhysRevB.84.033407. URL http://link.aps.org/doi/10.1103/PhysRevB.84.033407.

- (23) Archana Venugopal. Effect of contacts, graphene type and underlying substrate on the transport properties of graphene. 2012.

- (24) A. C. Ferrari, J. C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscanec, D. Jiang, K. S. Novoselov, S. Roth, and A. K. Geim. Raman spectrum of graphene and graphene layers. *Phys. Rev. Lett.*, 97:187401, Oct 2006. doi: 10.1103/PhysRevLett.97. 187401.

- (25) Jeong-Yuan Hwang, Chun-Chiang Kuo, Li-Chyong Chen, and Kuei-Hsien Chen. Correlating defect density with carrier mobility in large-scaled graphene films: Raman spectral signatures for the estimation of defect density. *Nanotechnology*, 21(46):465705, 2010.

- (26) K Nagashio, T Nishimura, K Kita, and A Toriumi. Contact resistivity and current flow path at metal/graphene contact. *Applied Physics Letters*, 97(14):143514, 2010.

- (27) Mike Zhu Matt Hollander Richard Kasarda et al. Joshua A. Robinson, Michael LaBella. Contacting graphene. *Appl. Phys. Lett.*, 98:053103, 2011. doi: http://dx.doi.org/10.1063/1. 3549183.

- (28) Ferney A. Chaves, David JimÃČÂl'nez, Aron W. Cummings, and Stephan Roche. Physical model of the contact resistivity of metal-graphene junctions. *Journal of Applied Physics*, 115(16):164513, 2014. doi: http://dx.doi.org/10.1063/1.4874181. URL http://scitation.aip.org/content/aip/journal/jap/115/16/10.1063/1.4874181.

- (29) Simon M Sze and Kwok K Ng. *Physics of semiconductor devices*. John Wiley & Sons, 2006.