# Transfer Printing of CVD Graphene FETs on Patterned Substrates

T. S. Abhilash<sup>1</sup>, R. De Alba<sup>1</sup>, N. Zhelev<sup>1</sup>, H. G. Craighead<sup>2</sup> and J. M. Parpia<sup>1,a</sup>

<sup>1</sup>Department of Physics, Cornell University, Ithaca, New York 14853, USA.

<sup>2</sup>School of Applied and Engineering Physics, Cornell University, Ithaca, New York 14853, USA.

We describe a simple and scalable method for the transfer of CVD graphene for the fabrication of field effect transistors. This is a dry process that uses a modified RCA-cleaning step to improve the surface quality. In contrast to conventional fabrication routes where lithographic steps are performed after the transfer, here graphene is transferred to a pre-patterned substrate. The resulting FET devices display nearly zero Dirac voltage, and the contact resistance between the graphene and metal contacts is on the order of 910  $\pm$  340  $\Omega$   $\mu m$ . This approach enables formation of conducting graphene channel lengths up to one millimeter. The resist-free transfer process provides a clean graphene surface that is promising for use in high sensitivity graphene FET biosensors.

a) jmp9@cornell.edu

### I. INTRODUCTION

Graphene, a single planar sheet of carbon atoms has attracted great attention due to its remarkable electrical properties<sup>1</sup>. Large area graphene channel field effect transistors (FET) with pristine surfaces (as characterized by a Dirac voltage close to zero gate-bias), with low noise, and operated in liquid-gating mode, are attractive for biosensing applications<sup>2-7</sup>. Graphene grown through chemical vapor deposition (CVD)<sup>8,9</sup> can be employed for scaling up graphene channel devices to arbitrarily large dimensions. By scaling up the sensor size, the baseline noise level can be reduced<sup>5, 10</sup> and the devices can be easily adapted for liquid-gated bio sensing applications. Methodologies currently used to transfer CVD graphene require wet chemical etching of the metal substrate on which the graphene is grown and involve the use of polymethylmethacrylate (PMMA) as a support layer to facilitate transfer to the target substrate. This process is problematic for two reasons: 1) The etching process can produce residues that become trapped at the graphene-substrate interface. 2) The use of PMMA introduces contaminates on the topside graphene surface, degrading the electrical performance of the transistors. Moreover, to fabricate devices in the conventional process, graphene is transferred first followed by the patterning of electrical contacts. Patterning exposes the graphene to polymers that necessitate additional cleaning steps to achieve desirable electrical properties such as a low gate voltage at which the minimum conductance ("Dirac peak") is manifested. A high quality transfer of CVD graphene for FETs has been demonstrated using a modified-Radio Corporation of America (RCA) cleaning method that removes contaminations from the conventional wet chemical etching transfer method<sup>11</sup>. Though this approach provides a clean graphene-substrate interface, it requires the use of a polymer layer to achieve both the transfer of the graphene and the subsequent patterning of electrical contacts. Imperfect removal of the polymer from the top-side of the graphene often results in a residue that compromises the graphene surface quality and the electrical characteristics of the resulting transistor-device. Annealing at high temperature in a H<sub>2</sub>/Ar atmosphere can remove most of the polymer<sup>12-14</sup>, but the trace residues result in variable and often large values of the gate voltage at which the Dirac peak is observed. These characteristics limit the sensitivity of graphene-based sensors<sup>2-7</sup>. Thus it was seen to be desirable when devising high sensitivity graphene sensors to develop a 'resist-free' approach for both the graphene transfer and post transfer processes.

Dry transfer of graphene using polydimethylsiloxane (PDMS)<sup>15-22</sup>, thermal release tape<sup>23-25</sup>, electrostatic process<sup>26</sup> and pressure sensitive adhesive<sup>27</sup> have also been reported. Although dry transfer printing of graphene can provide a nearly contamination-free surface, again these approaches require post-transfer patterning and exposure to resists. In this paper we report a reliable method for CVD graphene transfer, using a combination of dry transfer by PDMS, and a modified-RCA-cleaning approach. In contrast to the previous reports, we employ PDMS assisted graphene transfer to pre-patterned source-drain electrodes on Si/SiO<sub>2</sub> wafers, which circumvents contact between lithographic resists and graphene. This method is scalable and graphene channel FETs with channel lengths as large as one millimeter can be fabricated. Transistor transfer characteristics (source–drain conductance versus back gate voltage) exhibit a clear Dirac peak close to zero back gate voltage. Morphology analysis of graphene after transfer, using Atomic Force Microscopy (AFM), Raman spectroscopy and Scanning Electron microscopy (SEM), confirm the presence of a clean graphene monolayer transferred onto the

substrate. The contact resistance (R<sub>c</sub>) between graphene and array of Ti/Au metal contacts is on the order of 910  $\pm$  340  $\Omega$   $\mu m$  .

### II. EXPERIMENTAL

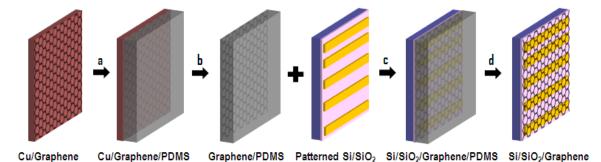

Our graphene transfer process is schematically depicted in Fig. 1. It begins with the growth of graphene films on Cu foils using CVD<sup>8, 9</sup> and the films obtained were characterized by SEM and Raman spectroscopy. The carbon deposition on the back-side of copper foil was removed by etching using oxygen plasma. Self-prepared PDMS as well as commercially available PDMS (thickness ~50 µm) material (Gelfilm from Gelpak) were used for the graphene transfer with equal success. The Cu/graphene stack was placed on a PDMS block, with the graphene face in contact with the PDMS. The copper foil was gently pressed using a Teflon roller to adhere the graphene face to the PDMS.

Fig.1: Schematic illustration of CVD graphene transfer process: a) Adhesion of Cu/graphene to PDMS, b) Etching of the Cu, c) Attachment of graphene/PDMS to  $Si/SiO_2$ , d) PDMS removal. After the copper is etched, a modified-RCA process was carried out to clean the graphene-Cu interface, and then graphene films were transferred onto a source-drain patterned  $Si/SiO_2$  wafer.

After adhesion of the PDMS, the Cu/graphene/PDMS assembly was immersed in Cu etchant (HCl/FeCl<sub>3</sub> solution in water) for an hour, to etch the copper foil, followed by a repeated rinsing with deionized (DI) water. The resulting graphene/PDMS assembly

was further subjected to a modified-RCA cleaning process to remove etch residues and metal particles<sup>11</sup>. First, the assembly was placed in HCl/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O solution (volume ratio 1: 1: 20) for 15 min, followed by a thorough rinsing with DI-water. Then the graphene/PDMS was transferred to a NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O solution (volume ratio 1:1:20) for 15 minutes, followed by a second rinse with DI-water. Finally, the graphene/PDMS assembly was attached to a target Si/SiO<sub>2</sub> substrate with the graphene facing the prepatterned metal contacts. The whole assembly was heated to 140°C for 10 minutes. The PDMS layer was removed by immersing the PDMS/graphene/SiO<sub>2</sub>/Si assembly in methylene chloride. This step was followed by rinsing the graphene/SiO<sub>2</sub>/Si with DI-water, and a final blow-drying step to complete the transfer.

The graphene-channel FETs were formed by depositing the graphene onto gold source and drain electrodes, pre-patterned on a p-doped Si wafer. The underlying Si serves as a universal back-gate, with 300nm of thermally grown SiO<sub>2</sub> isolating it from the conduction and gate channels. Using standard photo-lithographic techniques, source and drain electrodes were patterned with the distance between source-drain electrodes varied from 50 µm to a few millimeters. Titanium (10 nm) and gold (40 nm) were used for source-drain contact metallization. The device design and circuit diagram used for the electrical characterization are given in section 1 of the supplementary information. Electrical measurements were performed at room temperature under ambient conditions.

Contact resistance values are generally measured using a transfer length measurement (TLM) method<sup>28</sup>. We fabricated a TLM structure with varying channel lengths (5 to 30  $\mu$ m in steps of 5  $\mu$ m) on a Si/SiO<sub>2</sub> wafer using Ti/Au metal contacts. Graphene was stamped over the array after carrying out the cleaning by following our

modified-RCA method described earlier. Then the graphene was etched to obtain a rectangular sample of width (*W*) 50 µm as follows: a thin layer of aluminum (20 nm) was deposited on graphene to avoid direct contact with photoresist material. Then the photoresist was spin coated over the graphene-aluminum composite. Photolithography was used to define the channel region, exposing the resist and aluminum. The exposed resist and aluminum was removed by developer solution and the exposed graphene was etched using oxygen plasma. Finally, the aluminum and resist on top of the graphene layer were removed by flood exposure and subsequent treatment with developer solution. This method did not introduce additional contaminants in the graphene channel.

### **RESULTS AND DISCUSSION**

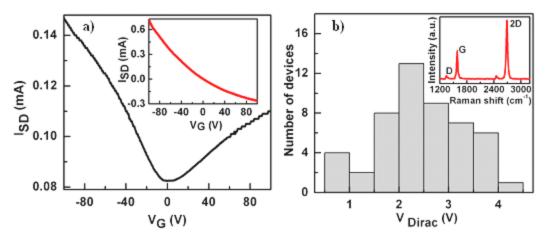

The devices were electrically characterized by measuring source-drain current ( $I_{SD}$ ) as function of back gate bias ( $V_G$ ) for fixed source-drain voltage ( $V_{SD}$  = 50 mV). The gating curve for a device transferred after the use of a conventional Cu etching method, without the modified-RCA cleaning step is shown in the inset of Fig. 2a. The absence of the Dirac peak is an indication that the graphene layer is highly contaminated. Devices fabricated with the commonly used wet transfer method, where the graphene/polymer stack is scooped up over pre-patterned electrodes after the modified-RCA cleaning steps, also showed a similar response. In contrast, the dry transfer of graphene films to the patterned substrate (and subsequent modified-RCA cleaning) consistently produces devices with low Dirac voltages (Fig. 2a, 2b). This indicates that devices prepared in this fashion are much cleaner than those transferred without modified-RCA cleaning or by the conventional process.

Fig. 2: a) Current-gate voltage  $(I_{SD}-V_G)$  characteristic measurement of a device fabricated with graphene dry transfer and after modified-RCA cleaning. The source-drain spacing of the device used is 50  $\mu$ m. Inset shows  $I_{SD}-V_G$  for a device fabricated by conventional Cu etching method. b) Distribution of the voltage of Dirac points of devices fabricated from dry transferred graphene and by using modified-RCA cleaning steps. All devices exhibit their Dirac peak at less than 4.5 volts gate-bias. Inset shows Raman spectrum indicating the transfer of monolayer graphene films to Si/SiO<sub>2</sub> substrate.

The reproducibility of the low Dirac voltage was analyzed by measuring 50 devices and the distribution of the observed Dirac voltages is shown in Fig 2b. Dirac voltages were confined to a window of 0.5 to 4.5 V, indicating a narrow distribution. The typical Raman spectrum of a device is shown in Fig. 2b inset. The location and intensity of the characteristic G and 2D peaks signifies the presence of monolayer graphene. The field effect mobility ( $\mu$ ) was extracted using the relationship  $\mu = (L/WC_GV_{SD})$  ( $\Delta I_{SD}/\Delta V_G$ ), where L and W are the graphene channel length (50  $\mu$ m) and width (50  $\mu$ m) respectively and  $C_G$  is the gate capacitance (11.6 nF/cm<sup>2</sup> for 300 nm SiO<sub>2</sub>). Under ambient conditions, a mobility of 1240 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> was observed. Although the mobility is lower than the best reported mobility of CVD grown graphene<sup>29</sup>, it is comparable with the devices fabricated via the modified-RCA cleaning method<sup>11</sup>.

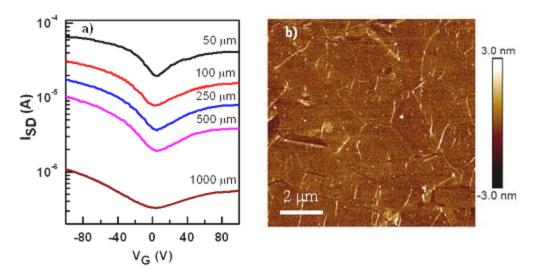

Fig. 3: a) Gating curves of graphene FET array with channel lengths  $50-1000 \mu m$ . b) AFM image of graphene film transferred on  $Si/SiO_2$  substrate.

Though methods are well established for growing graphene over large length scale by  $\text{CVD}^{8, 9}$ , most devices have been limited to micrometer lengths<sup>5, 6</sup>. In order to explore the possibility of large-area device fabrication for improved (bio) sensing, where a shift in Dirac peak gate voltage is monitored, FETs were made using the transfer method described above while scaling-up the graphene channel length from 50  $\mu$ m to several millimeters. Fig. 3a shows  $I_{SD}$ - $V_{G}$  measured in a graphene FET device array for different channel lengths. All the devices with a channel length up to 1000  $\mu$ m show a Dirac peak, and  $V_{Dirac}$  is observed at less than 4 V gate-biases across the array. The morphology of the graphene film on the  $\text{Si/SiO}_2$  substrate was analyzed using AFM and the image obtained (area:  $10 \ \mu\text{m}^2$ ) is shown in Fig. 3b. From the image, the surface is found to be nearly flat with a surface roughness of about  $\pm$  3 nm. Rips and wrinkles in the transferred graphene are observed, but the graphene sheet is electrically continuous over lengths exceeding one millimeter. The rips and wrinkles may have occurred during

Cu/graphene/PDMS assembly preparation step. Surface analysis was done using SEM, and a similar morphology was observed (see section 2 of supplementary information).

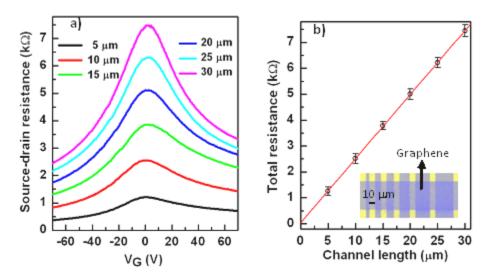

Fig. 4: a) Total resistance between source and drain electrodes in a graphene FET array as a function of back gate bias. Dirac voltage occurs at a gate bias of  $3 \pm 0.5$  V. b)  $R_{total}$  vs. channel length changing from 5-30  $\mu m$ , at  $V_G=3$  V. Black circles indicate total resistance and red line represents the linear fit. Inset shows SEM image (false color) of a graphene FET array used for study.

The methodology followed in the majority of reported works (that measure the electrical properties of graphene) involve the transfer of graphene followed by deposition of the metal contacts. In contrast, one of the novelties of our method lies in the transfer of graphene on to pre-patterned metal contacts. The benefit of this approach compared to the reported methods was evaluated by measuring the metal-graphene contact resistance. Fig. 4a represents the  $I_{SD}$ - $V_G$  measurements with different channel lengths. The total resistance reaches the maximum value at Dirac point, and it is observed at a back gate bias of  $\sim 3 \pm 0.5$  volts across the array. A plot of source-drain resistance ( $R_{total}$ ) at the Dirac point as a function of varying channel length is shown in Fig. 4b. It showed a linear behavior and the intercept at zero channel length =  $2R_c$  ( $36.4 \pm 13.6 \Omega$ ) is obtained. The

sheet resistance (Rs) can be extracted from the slope of a linear fit, and was found to be  $12.4 \; k\Omega/\square.$

There are various reports on contact resistance measurement in graphene channel field effect transistors  $^{30\text{-}33}$ . Depending on many factors such as fabrication schemes, type of metal used, gate bias voltage and measurement conditions, the reported normalized contact resistance ( $R_cW$ ) values vary from  $100~\Omega~\mu m$  to few  $k\Omega~\mu m$ . In comparison to the  $R_cW$  values reported, our fabrication method, where graphene is transferred onto a prepatterned substrate yields a value for  $R_cW=910\pm340~\Omega~\mu m$  for a Ti/Au contact. This value is lower than most reported. Another advantage of the described method is that it does not require post fabrication steps like thermal and current annealing.

## **III. CONCLUSION**

We have demonstrated a simple, scalable CVD graphene transfer method employing a combination of dry transfer and modified-RCA cleaning methods. In contrast with the conventional fabrication approach, graphene was transferred to a prepatterned substrate. FET devices exhibited Dirac voltage close to zero gate bias, and the contact resistance between the graphene and metal was measured as 910  $\pm$  340  $\Omega$   $\mu m$ . This approach enables the FET channel length to be scaled up to devices of length one millimeter. Also, the absence of any resist layers during fabrication steps guarantees a cleaner graphene surface as characterized by a low  $V_G$  at which the Dirac peak occurs. Chemical and bio-sensors which rely on the shift of the  $V_G$  associated with the Dirac peak would benefit from the device characteristics obtained by following our improved procedure.

#### **ACKNOWLEDGMENTS**

We acknowledge the support of the staff and use of the facilities of the Cornell NanoScale Science and Technology Facility. T.S.A. would like to thank Vinayakan Ramachandran Nair, AEP, Cornell University for fruitful discussions. We also acknowledge the financial support from the Cornell Center for Materials Research under DMR 1120296 and by the NSF under DMR1202991.

#### **REFERENCES**

- 1) A.K. Geim, K. S. Novoselov, Nat. Mater. 6, 183 (2007).

- M. B. Lerner, F. Matsunaga, G. H. Han, S. J. Hong, J. Xi, A. Crook, J. M. P. Aguilar,

Y. W. Park, J. G. Saven, R. Liu, A. T. C. Johnson, Nano Lett. 14, 2709 (2014).

- 3) B. M. Dankerl, M. V. Hauf, A. Lippert, L. H. Hess, S. Birner, Ian D. Sharp, A. Mahmood, P. Mallet, J. Y. Veuillen, M. Stutzmann, J. A. Garrido, Adv. Funct. Mater. **20**, 3117 (2010).

- 4) X. Dong, Y. Shi, Wei Huang, P. Chen, L. Jong Li, Adv. Mater. 22, 1649 (2010).

- 5) G. Saltzgaber, P. Wojcik, T. Sharf, M. R. Leyden, J. L. Wardini, C. A. Heist, A. A. Adenuga, V. T. Remcho, E. D. Minot, Nanotechnology **24**, 355502 (2013).

- 6) A. Kakatkar, T. S. Abhilash, R. De Alba, J. M. Parpia, H. G. Craighead, Nanotechnology **26**, 125502 (2015).

- 7) Y. Huang, X. Dong, Y. Shi, C. M. Li, L. J. Li, P. Chen, Nanoscale 2, 1485 (2010).

- 8) Li Xuesong, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, R. S. Ruoff, Science **324**, 1312 (2009).

- 9) Y. Hao, M. S. Bharathi, L. Wang, Y. Liu, H. Chen, S. Nie, X. Wang, H. Chou, C. Tan, B. Fallahazad, H. Ramanarayan, C. W. Magnuson, E. Tutuc, B. I. Yakobson, K. F. McCarty, Y. W. Zhang, P. Kim, J. Hone, L. Colombo, R. S. Ruoff, Science 342, 720 (2013).

- 10) Heller, S. Chatoor, J. Mannik, M. A. G. Zevenbergen, J. B. Oostinga, A. F. Morpurgo, C. Dekker, S. G. Lemay, Nano Lett. **10**, 1563 (2010).

- 11) X. Liang, B. A. Sperling, I. Calizo, G. Cheng, C. A. Hacker, Q. Zhang, Y. Obeng, K. Yan, H. Peng, Q. Li, X. Zhu, H. Yuan, A. R. H. Walker, Z. Liu, L. mao Peng, C. A.

- Richter, ACS Nano 5, 9144 (2011).

- 12) Y. Dan, Y. Lu, N. J. Kybert, Z. Luo, A. T. C. Johnson, Nano Lett. 9, 1472 (2009).

- 13) A. Pirkle, J. Chan, A. Venugopal, D. Hinojos, C. W. Magnuson, S. McDonnell, L. Colombo, E. M. Vogel, R. S. Ruoff, R. M. Wallace, Appl. Phys. Lett. 99, 122108 (2011).

- 14) S. Chen, W. Cai, D. Chen, Y. Ren, X. Li, Y. Zhu, J. Kang, R. S. Ruoff, New J. Phys. 12, 125011 (2010).

- 15) Y. Yu Wang, P. J. Burke, Appl. Phys. Lett. 103, 052103 (2013).

- K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J.-H. Ahn, P. Kim, J. Y. Choi, B. H. Hong, Nature 457, 706 (2009).

- M. J. Allen, V. C. Tung, L. Gomez, Z. Xu, L.-M. Chen, K. S. Nelson, C. Zhou, R. B. Kaner, Y. Yang, Adv. Mater. 21, 2098 (2009).

- 18) Y. Lee, S. Bae, H. Jang, S. Jang, S.-E. Zhu, S. H. Sim, Y. Il Song, B. H. Hong, J. H. Ahn, Nano Lett. **10**, 490 (2010).

- 19) T. Oznuluer, E. Pince, E. O. Polat, O. Balci, O. Salihoglu, C. Kocabas, Appl. Phys. Lett. **98**, 183101 (2011).

- 20) S. J. Kang, B. Kim, K. S. Kim, Y. Zhao, Z. Chen, G. H. Lee, J. Hone, P. Kim, C. Nuckolls, Adv. Mater. **23**, 3531 (2011).

- 21) J. Song, F.Y. Kam, R.Q. Png, W.L. Seah, J.M. Zhuo, G.K. Lim, P. K. H. Ho, L. L. Chua, Nat. Nanotechnol. **8**, 356 (2013).

- 22) C. Y. Su, D. Fu, A. Y. Lu, K. K. Liu, Y. Xu, Z. Y. Juang, L. J. Li, Nanotechnology **22**, 185309 (2011).

- 23) S. Bae, H. Kim, Y. Lee, X. Xu, J. S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H. R. Kim, Y. Song, Y. J. Kim, K. S. Kim, B. Ozyilmaz, J. H. Ahn, B. H. Hong, S. Iijima, Nat. Nanotechnol. 5, 574 (2010).

- 24) Y. Lee, S. Bae, H. Jang, S. Jang, S. E. Zhu, S. H. Sim, Y. Song, B. H. Hong, J. H. Ahn, Nano Lett. **10**, 490 (2010).

- 25) J. D. Caldwell, T. J. Anderson, J. C. Culbertson, G. G. Jernigan, K. D. Hobart, F. J. Kub, M. J. Tadjer, J. L. Tedesco, J. K. Hite, M. A. Mastro, R. L. M. Ward, C. R. Eddy, P. M. Campbell, and D. K. Gaskill, ACS Nano 4, 1108 (2010).

- 26) D. Y. Wang, I. S. Huang, P. H. Ho, S. S. Li, Y. C. Yeh, D. W. Wang, W. L. Chen, Y.Y. Lee, Y. M. Chang, C. C. Chen, C. T. Liang, C. W. Chen, Adv. Mater. 25, 4521 (2013).

- 27) S. J. Kim, T. Choi, B. Lee, S. Lee, K. Choi, J. B. Park, J. M. Yoo, Y. S. Choi, J. Ryu, P. Kim, J. Hone, B. H. Hong, Nano Lett. 15, 3236 (2015).

- 28) S. S. Cohen, Thin Solid Films 104, 361 (1983).

- 29) Xuesong Li, C. W. Magnuson, A. Venugopal, J. An, J. W. Suk, B. Han, M. Borysiak, W. Cai, A. Velamakanni, Y. Zhu, L. Fu, E. M. Vogel, E. Voelk, L. Colombo, R. S. Ruoff, Nano Lett. 10, 4328 (2010)

- 30) A. Venugopal, L. Colombo, E. M. Vogell, Appl. Phys. Lett. 96, 013512 (2010).

- 31) F. Xia, V. Perebeinos, Y. M. Lin, Y. Wu, P. Avouris, Nat. Nanotechnol. 6, 179 (2011).

- 32) E. Watanabe, A. Conwill, D. Tsuya, Y. Koide, Diamond & Related Materials **24**, 171 (2012).

- 33) W. S. Leong, H. Gong, J. T. L. Thong, ACS Nano 8, 994 (2014).